# AN ASYNCHRONOUS DMA CONTROLLER

A THESIS SUBMITTED TO THE UNIVERSITY OF MANCHESTER

FOR THE DEGREE OF MASTER OF PHILOSOPHY

IN THE FACULTY OF SCIENCE AND ENGINEERING

January 1999

By

Chatchai Jantaraprim

Department of Computer Science

# Contents

| A                | bstac                   | et .                            | 10 |  |  |  |

|------------------|-------------------------|---------------------------------|----|--|--|--|

| $\mathbf{D}_{i}$ | Declaration 1 Copyright |                                 |    |  |  |  |

| C                |                         |                                 |    |  |  |  |

| D                | Dedication 1            |                                 |    |  |  |  |

| $\mathbf{A}$     | ckno                    | m wledgements                   | 14 |  |  |  |

| 1                | DMA Controllers         |                                 |    |  |  |  |

|                  | 1.1                     | Introduction                    | 15 |  |  |  |

|                  | 1.2                     | Existing DMA controllers        | 18 |  |  |  |

|                  |                         | 1.2.1 8237 Intel DMA controller | 18 |  |  |  |

|                  |                         | 1.2.2 National's NS32230        | 20 |  |  |  |

|                  | 1.3                     | Summary                         | 21 |  |  |  |

| 2                | $\mathbf{Asy}$          | nchronous Logic Design          | 22 |  |  |  |

|                  | 2.1                     | Introduction                    | 22 |  |  |  |

|   | 2.2 | Asynchronous logic design                 | 25         |

|---|-----|-------------------------------------------|------------|

|   | 2.3 | Micropipelines                            | 27         |

|   | 2.4 | The AMULET Processors                     | 28         |

|   | 2.5 | Summary                                   | 30         |

| 3 | The | AMULET3i Subsystem                        | 31         |

|   | 3.1 | Introduction                              | 31         |

|   | 3.2 | The MARBLE Bus                            | 32         |

|   |     | 3.2.1 Initiator Interface                 | 33         |

|   |     | 3.2.2 Target Interface                    | 34         |

|   |     | 3.2.3 Type of data transfer               | 35         |

|   | 3.3 | Processor-Memory Subsystem                | 36         |

|   |     | 3.3.1 The AMULET3 Processor Core          | 36         |

|   |     | 3.3.2 Local RAM                           | 37         |

|   |     | 3.3.3 The Processor Local Buses           | 37         |

|   | 3.4 | Other Devices                             | 38         |

|   |     | 3.4.1 On-chip ROM                         | 38         |

|   |     | 3.4.2 External Memory Interface           | 38         |

|   |     | 3.4.3 The Asynchronous Peripheral Devices | 38         |

|   |     | 3.4.4 Test Interface Controller           | 39         |

|   | 3.5 | The DMA Controller                        | 39         |

| 1 | Top | Loyal Dasign                              | <i>1</i> ( |

|   |     |                                                                                                                                                                                         | ŀU             |

|---|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

|   | 4.2 | Specifications                                                                                                                                                                          | :0             |

|   | 4.3 | The DMA operation overview                                                                                                                                                              | :1             |

|   | 4.4 | The DMA controller internal structure                                                                                                                                                   | 2              |

|   | 4.5 | The Register Unit                                                                                                                                                                       | 2              |

|   |     | 4.5.1 The Global Register Unit                                                                                                                                                          | :3             |

|   |     | 4.5.2 The Channel Registers                                                                                                                                                             | :5             |

|   | 4.6 | The Transfer Engine Unit                                                                                                                                                                | :8             |

|   |     | 4.6.1 The Channel Arbiter Unit                                                                                                                                                          | :8             |

|   |     | 4.6.2 The Transfer Control Unit                                                                                                                                                         | 0              |

|   | 4.7 | Summary                                                                                                                                                                                 | 0              |

| 5 | Des | ign Issues 5                                                                                                                                                                            | <b>2</b>       |

|   | 5.1 | Introduction                                                                                                                                                                            | 2              |

|   |     |                                                                                                                                                                                         |                |

|   | 5.2 | DMA Registers                                                                                                                                                                           | 2              |

|   | 5.2 | DMA Registers                                                                                                                                                                           |                |

|   | 5.2 |                                                                                                                                                                                         | 53             |

|   | 5.2 | 5.2.1 Transfer Control Configurations                                                                                                                                                   | 53             |

|   |     | 5.2.1 Transfer Control Configurations                                                                                                                                                   | 54<br>54       |

|   |     | 5.2.1 Transfer Control Configurations 5   5.2.2 Processor Interrupt Control Configuration 5   DMA Operation 5   5.3.1 DMA Operation Overview 5                                          | 54<br>54       |

|   |     | 5.2.1 Transfer Control Configurations55.2.2 Processor Interrupt Control Configuration5DMA Operation55.3.1 DMA Operation Overview55.3.2 Channel Selection5                               | 53<br>54<br>54 |

|   |     | 5.2.1 Transfer Control Configurations55.2.2 Processor Interrupt Control Configuration5DMA Operation55.3.1 DMA Operation Overview55.3.2 Channel Selection55.3.3 Data Transfer Operation5 | 53<br>54<br>54 |

|   | 0.4   | Shared | d resources in the DMA controller                                                                      | 01         |

|---|-------|--------|--------------------------------------------------------------------------------------------------------|------------|

|   |       | 5.4.1  | Dual-Ported Memory                                                                                     | 62         |

|   |       | 5.4.2  | Registers locking                                                                                      | 62         |

|   |       | 5.4.3  | Arbitration                                                                                            | 63         |

|   | 5.5   | Arbitr | ration                                                                                                 | 63         |

|   |       | 5.5.1  | MARBLE Arbitration                                                                                     | 64         |

|   |       | 5.5.2  | DMA Registers Arbitration                                                                              | 64         |

|   |       | 5.5.3  | Channel Arbitration                                                                                    | 65         |

|   |       | 5.5.4  | Arbitrated-Call                                                                                        | 70         |

|   | 5.6   | Proble | ${ m ems}$                                                                                             | 71         |

|   |       | 5.6.1  | Deadlock                                                                                               | 71         |

|   |       | 5.6.2  | Race condition                                                                                         | 72         |

|   | 5.7   | Synch  | ${\it ronization} \ \ldots \ $ | 73         |

|   |       | 5.7.1  | Peripheral Synchronization                                                                             | 74         |

|   |       | 5.7.2  | Processor Synchronization                                                                              | 75         |

|   | 5.8   | Summ   | nary                                                                                                   | 75         |

| c | D - 1 | . •    | 1 D/C- J-1-                                                                                            | <b>=</b> 0 |

| 6 | веп   | aviour | cal Models                                                                                             | 76         |

|   | 6.1   | Introd | luction                                                                                                | 76         |

|   | 6.2   | Model  | lling tools                                                                                            | 77         |

|   | 6.3   | Simpli | ified models                                                                                           | 78         |

|   | 6.4   | AMUI   | LET3i DMA Controller Model                                                                             | 79         |

|   | 6.5   | Model  | of the Registers                                                                                       | 80         |

|    |       | 6.5.1  | Global Registers                | 80 |

|----|-------|--------|---------------------------------|----|

|    |       | 6.5.2  | Channel Registers               | 81 |

|    | 6.6   | Model  | of the Transfer Engine          | 81 |

|    |       | 6.6.1  | Transfer Control Module         | 82 |

|    |       | 6.6.2  | Channel Arbiter                 | 82 |

|    | 6.7   | Simula | ation Schemes                   | 82 |

|    | 6.8   | Simula | ation Results                   | 83 |

|    |       | 6.8.1  | Deadlock                        | 83 |

|    |       | 6.8.2  | Early Interrupt Request Sending | 84 |

|    |       | 6.8.3  | Race Condition                  | 86 |

|    | 6.9   | Summ   | ary                             | 89 |

| 7  | Con   | clusio | ns                              | 90 |

|    | 7.1   | The A  | MULET3i DMA Controller          | 90 |

|    | 7.2   | Conclu | isions                          | 91 |

| Bi | bliog | graphy |                                 | 94 |

|    |       | , 1 /  |                                 |    |

# List of Tables

# List of Figures

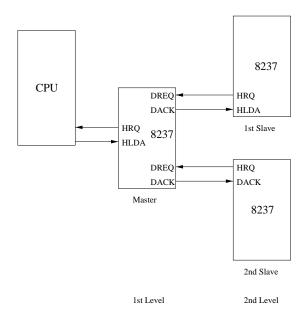

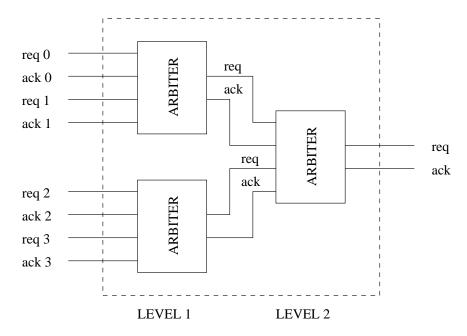

| 1.1 | 8237 in cascade mode                                | 19 |

|-----|-----------------------------------------------------|----|

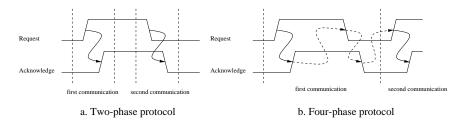

| 2.1 | Signalling protocols                                | 26 |

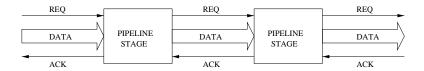

| 2.2 | Simple structure of Micropipelines                  | 28 |

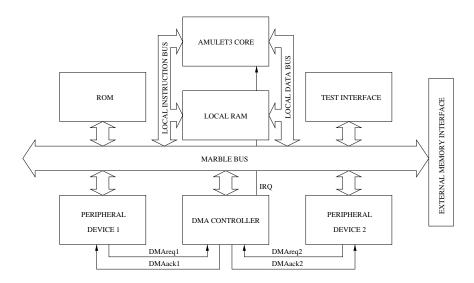

| 3.1 | The AMULET3i Subsystem                              | 32 |

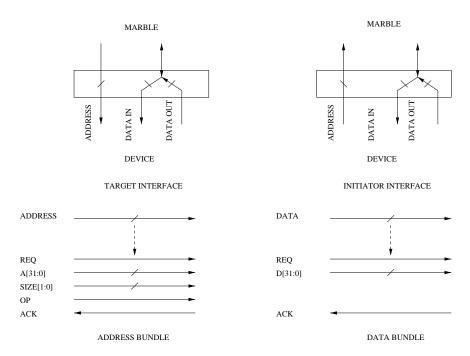

| 3.2 | The MARBLE interfaces                               | 33 |

| 3.3 | Initiator interface data transfer operations        | 34 |

| 3.4 | Target interface data transfer operations           | 35 |

| 4.1 | Block diagram of the DMA controller                 | 43 |

| 4.2 | Register Unit                                       | 44 |

| 4.3 | Global Registers                                    | 45 |

| 4.4 | Channel Registers                                   | 46 |

| 4.5 | Control Register                                    | 47 |

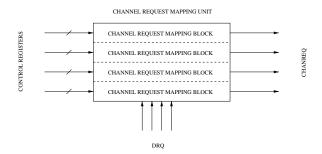

| 4.6 | Channel Request Mapping Unit                        | 47 |

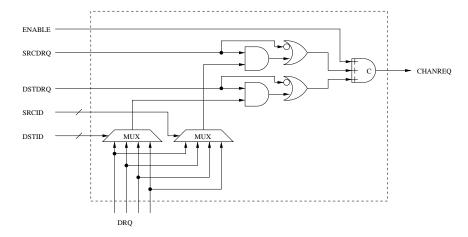

| 4 7 |                                                     |    |

| 4.7 | Internal structure of Channel Request Mapping Block | 48 |

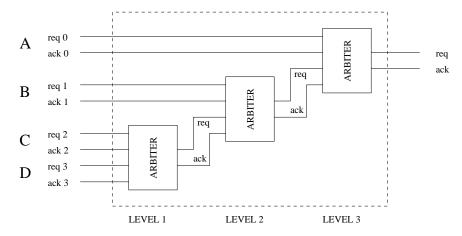

| 4.9  | Channel Arbiter Unit                                        | 49 |

|------|-------------------------------------------------------------|----|

| 5.1  | Sequence of the DMA operation                               | 55 |

| 5.2  | Register communication with wide bus                        | 58 |

| 5.3  | Register communication with narrow bus                      | 60 |

| 5.4  | Global Registers Arbitration                                | 65 |

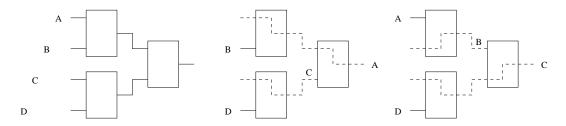

| 5.5  | Balanced arbitration tree                                   | 66 |

| 5.6  | Balanced tree order of gaining access                       | 67 |

| 5.7  | Unbalanced arbitration tree                                 | 68 |

| 5.8  | Unbalanced arbitration tree                                 | 69 |

| 5.9  | System Deadlock Problem                                     | 72 |

| 5.10 | Peripheral Request Handshake                                | 74 |

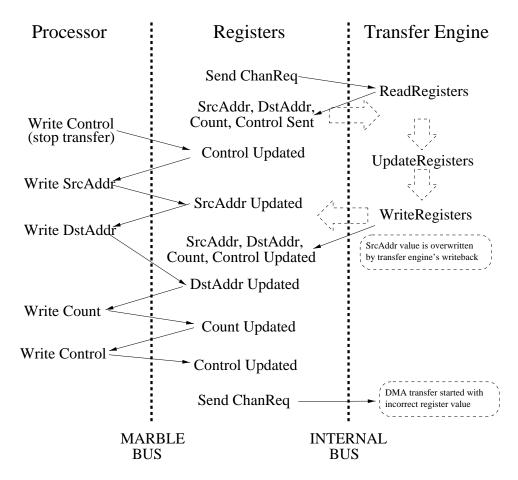

| 6.1  | Deadlock cause by atomic register access by transfer engine | 84 |

| 6.2  | Non-atomic register access solve the deadlock problem       | 85 |

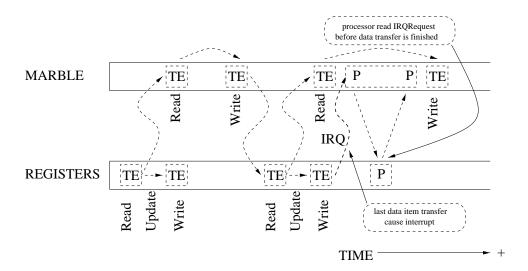

| 6.3  | Early interrupt sending                                     | 85 |

| 6.4  | Delay registers write back for last data transfer           | 86 |

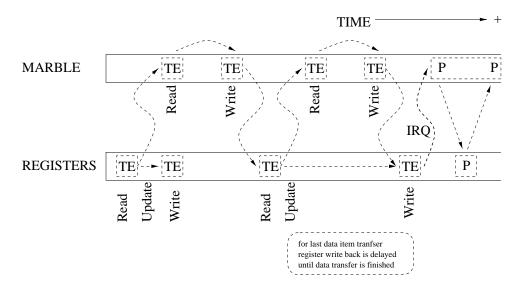

| 6.5  | Race Condition                                              | 87 |

| 6.6  | Using a flag to prevent Race Condition                      | 88 |

# **Abstact**

An asynchronous Direct-Memory-Access (DMA) controller for an asynchronous microprocessor subsystem has been designed. Behavioural modelling and simulation of the DMA controller was performed using LARD, a hardware description language for asynchronous logic design. Problems in designing the DMA controller using an asynchronous logic design methodology are discussed, and solutions to these problems are presented.

# **Declaration**

No portion of the work referred to in this thesis has been submitted in support of an application for another degree or qualification of this or any other university or other institution of learning.

# Copyright

Copyright in text of this thesis rests with the Author. Copies (by any process) either in full, or of extracts, may be made **only** in accordance with instructions given by the Author and lodged in the John Rylands University Library of Manchester. Details may be obtained from the Librarian. This page must form part of any such copies made. Further copies (by any process) of copies made in accordance with such instructions may not be made without the permission (in writing) of the Author.

The ownership of any intellectual property rights which may be described in this thesis is vested in the University of Manchester, subject to any prior agreement to the contrary, and may not be made available for use by third parties without the written permission of the University, which will prescribe the terms and conditions of any such agreement.

Further information on the conditions under which disclosures and exploitation may take place is available from the head of Department of Computer Science.

# Dedication

To HangChee & HYingKlang, with love.

# Acknowledgements

Thanks a lot for being my supervisor and not given up reading/correcting/ trying to understand those rubbish I wrote in my thesis and show me the interesting bits in the asynchronous logic design, thank you, Jim.

Thanks being friends, correcting my English, playing games, opening the world of asynchronous logic design to me, and most of all giving me the most enjoys moment of living here, my dear friends and brothers, Andrew and John.

Thanks for advising, giving the 'stucture' to my thesis, running, orienteering, trailquest, (un-successful) uni-cycling, and inspires my juggling, Doug.

Thanks a lot to Chung for those several interesting discussions, even though many of them I don't agree with you, but it is still interesting anyway.

Thanks a lot to Phil, for LARD, that is where I started.

Thanks a lot to all of AMULET people for these more than two years of companion.

# Chapter 1

## **DMA** Controllers

## 1.1 Introduction

In a computer system, the processor spends considerable time moving data around, though it does not perform this very efficiently. In order to transfer a single datum, a processor has to fetch instructions from memory, decode and execute these instructions and in addition to performing the transfer. A simple data transfer operation such as read/write a block of data from/to a peripheral device can burden the processor in fetching, decoding and executing instructions most of the time instead of performing actual data transfer.

An autonomous computer device which could be used to relieve the processor from this task is a Direct-Memory-Access (DMA) controller. A DMA controller is a simplified processor which can only perform the function of data transfer between devices. It need not be able to perform any other functions, such as reading and interpreting instructions, so it can work faster and more efficiently than the central processor.

A DMA controller, after being programmed, can perform data transfers without processor intervention. The processor is then free, while DMA transfers are in progress, to perform other functions. The data transfer process may also be faster and use less power since the DMA controller need not fetch, decode and execute instructions to perform the transfer.

A DMA controller can thus increase system performance and reduce power consumption (although the latter factor was not of much concern in the design of existing DMA controllers). A DMA controller would usually be used in small computer systems, e.g micro-computer, or engineering workstation [3, 5]; for larger computer systems, such as a super-computer, mainframe, or mini-computer, other kind of controllers or input/output processors are used to control data transfers, or handle input/output [16, 2, 18, 12].

Typically the DMA controller would be used to transfer data between a peripheral device and memory device, although memory to memory and peripheral to peripheral transfers are possible.

Data transfer between devices is usually done via a bus. This allows a device to transfer data to/from other devices without a direct connection with every device which would impose a high wiring cost when the number of devices is large. The bus simplifies connection between devices on the computer system.

Devices can be divided by behaviour into initiator devices and target devices. An initiator device is a device that can initiate a request to read/write data from/to another device, e.g. the processor or the DMA controller. A target device is one that sends or receives data when it receives read/write requests from another device, such as memory or peripheral device.

DMA controllers are both initiator and target devices. When a processor programs a DMA controller, the DMA controller receives values as a target device; when it performs autonomous DMA transfers, it behaves as an initiator.

Target devices can be divided by speed of response into "fast" and "slow" devices. A fast device, e.g. memory device, responds immediately when it receives a request from the initiator device. This kind of device stores data locally and usually is one built from electronic components instead of electro-mechanical components.

Slow devices might be built from electro-mechanical components, e.g. a hard

disk, or do not have data locally, e.g. communication devices. To read from or write to the slow target device, the initiator must wait until the target device is ready to transfer data or use some mechanism such as polling or interrupt to perform the transfer.

Waiting for the transfer is inefficient because this will occupy the bus for an indefinite period, bringing other system activity to a halt. In the polling scheme, the initiator device checks the status of the target device periodically until the target device is ready, before initiating the data transfer. With the interrupt scheme, the target device sends a notification signal (usually called an 'interrupt' when sending to the processor) to the initiator device when it is ready to perform a transfer.

In this approach the notification signal from target device can be regarded as a transfer request, but it is up to the initiator device to initiate read or write requests responding to the target device, alternatively the initiator can ignore this request from the target device.

To perform a DMA transfer, the DMA controller must be programmed with a source, a destination, an amount of data to be transfered, and other transfer control specifics such as whether the DMA controller should interrupt the processor or not when the transfer is finished, or the type of source and destination devices. The DMA controller can then perform the DMA transfer autonomously.

To perform each individual transfer the DMA controller must wait until transfer conditions are matched. These conditions are:

- The DMA was programmed and enabled by the processor

- Both source and destination devices are ready for transfer data

When both source and destination device are ready, the DMA controller reads data from the source device, writes it to the destination device, updates its pointers and counter and checks for conditions to stop the transfer. The DMA controller will normally repeat this process until a termination condition is matched,

and will notify the processor if required.

To transfer data with a slow peripheral device, an interrupt mechanism is used to notify the DMA controller when devices are ready to receive or transmit data. The interrupt signal from a device to the DMA controller is usually called 'DMA request'.

## 1.2 Existing DMA controllers

DMA controllers have been used in computer systems for many years. One of these designs [3] has been used in several generations of computers without any significant change in its specifications, except some speed enhancement to match faster system bus speeds.

Some of these designs' specifications have influenced the design of the asynchronous DMA controller that will be discussed this thesis. Two examples are given below.

#### 1.2.1 8237 Intel DMA controller

The Intel 8237, DMA controller, was designed to be used with Intel 80x86 microprocessor family, as used in the IBM PC and compatible computers. The original 8237 design was for an 8-bit data bus; a newer one supports a 16-bit data bus too. An 8237 has four independent DMA channels which are cascadable; a channel could be used to connect to another 8237 and expand the number of DMA channels in the system. The number of channels which can be used by cascading this DMA controller together is virtually unlimited. As shown in figure 1.1.

This DMA controller is designed specifically to transfer data between a peripheral device and a memory device. Transfer between memory devices is also supported, but two channels must be used together for this type of transfer. Peripheral to peripheral transfer is not supported. If the DMA controllers are cascaded one of channel is used for cascading and can't be used for DMA transfer.

Figure 1.1: 8237 in cascade mode

This DMA controller contains two set of registers which are used by the processor to program the DMA transfer characteristics. While a channel being transferred, the primary set of register is used, when the transfer finishes and if the secondary set of register was programmed by the processor, the DMA controller copy registers values from the secondary set to the primary set and continues. This allows the processor to program a DMA channel even though that channel is being used.

Each peripheral request signal is permanently fixed to a particular channel. The number of a peripheral device supported in the DMA transfer is hard-wired to a specific channel. Each channel has a 16-bit counter, so the maximum number of data it can transfer is 65536 items. Data transfer can be done only through the bus; data is read from source device to the DMA controller during the read-cycle and write from the DMA controller to the destination device during the write-cycle.

There are several variant of 8237 DMA controllers that are based on 8237 with some enhancements. In most recent PCs which use 80x86 processor and its variants, the 8237 DMA controller is part of the chipset on the mainboard [4].

#### 1.2.2 National's NS32230

The NS32230, National Semiconductor DMA controller, is designed to be used with NS32000 processor family.

Features of the NS32230 DMA controller:

• Transfer data between memory devices, between peripheral devices, as same as 'traditional' transfer data between memory and peripheral device.

#### • 8/16 bit transfer

Bus width for applications used NS32230. Transfer to/from 8-bit peripheral devices also support assembly/disassembly data 8-bit  $\langle - \rangle$  16-bit. Two 8-bit data reads from the peripheral device can be combined into 16-bit transfer for single write to 16-bit memory or peripheral device.

#### • Remote/local configuration

In remote configuration, the DMA controller and devices are connected to a dedicated bus and data transfer is performed on this bus. In local configuration the DMA controller and devices share the bus with the processor. In remote configuration, the processor can perform other functions which use the bus while the DMA transfer is in progress on its dedicated bus. However this needs a two bus system.

#### • Fly-past and store-and-forward transfers

In the store-and-forward data transfer, the operation is separated into read and write operations, the DMA controller performs two separate transaction on the bus; a read followed by a write. Another mechanism is fly-past transfer in which the DMA controller initiates both read and write requests simultaneously and the data is transferred directly from source device to destination device. Fly-past mechanism is faster at transferring data, but requires extra decode logic and cannot be used for memory to memory transfer on the same memory device. This DMA controller can support either mode of these.

#### • Command chaining

A channel can be chained to the next channel, when the data transfer is finished on the first channel, register values from the second channel will be copied to the first channel and the DMA controller can resume transfers on the first channel, allowing continuity in transfer for a specific device.

#### • Search capability

Data transfer functionality can be adapted to be used for other functions such as "on-the-fly" comparisons without adding much resource.

Interrupt vector generation

Common features in a mechanism to notify the processor after the transfer is finished.

## 1.3 Summary

DMA controller can provide a useful enhancement to a microprocessor system, relieving the CPU of consideration load and moving data faster and more efficiently than the CPU could alone. This has been exploited commercially for a long time, and some "standard" characteristics of DMA controllers have emerged.

The common features in these DMA controller are:

- Transfer function which can transfer between peripheral and memory, and between memory devices (even though it needs two channel to perform memory to memory transfer for 8237).

- Multiple-channels

- Several data sizes, to support different data width devices.

- Interrupt request to the processor when transfer is finished.

These functions of DMA controller are used as guideline to design the asynchronous DMA controller in this thesis.

# Chapter 2

# Asynchronous Logic Design

## 2.1 Introduction

In the field of digital circuit/logic design, two different design styles have been developed. These design styles, synchronous and asynchronous, were almost equally used at the beginning of digital logic design era, but synchronous logic design had been more favoured in the last few decades and become the accepted design style for complex circuits.

These two design styles differs from each other by the timing assumptions that are made. Synchronous logic assumes that time is discrete; each part of the system has to start and finish its tasks in the same period of time, Whereas asynchronous logic does not make any assumptions about timing; each part starts/stops working on its own.

In the synchronous logic design style, a clock, a periodic square wave signal, is used for global synchronization to specify when to start and finish tasks. Communication between any parts in the system must be done before end of a clock period when the whole system is synchronized. Synchronous logic design has been favoured by the chip design community for several decades because of several reasons [17]:

• It offers a simple way to design and test computing equipment

- It is widely taught and understood

- Parts that operates with clocks are widely available

- System noise has died away by the time a clock event occurs

Simplicity in timing models make synchronous logic design easier, especially when the circuits are not very complex, or no other constraints such as power consumption, performance, or electro-magnetic interference need to be considered.

With this simplicity, the development in circuit design has long been concentrated on the synchronous design style, and asynchronous design style has been virtually ignored.

As opposed to the synchronous logic design counterpart, the asynchronous logic design style is:

- Harder to design

- Not much taught or understood until recently

- Lacking components in standard libraries

- Short of development tools

- Overhead for simple circuit is higher

While the synchronous logic design uses a global signal for synchronization, the asynchronous logic design let circuits that need to communicate perform a local synchronization between themselves.

As circuits grow bigger and become more complex because of the need for higher performance and functionality, several problems caused by the timing assumption in synchronous logic design become more obvious. These problems are:

#### • Clock skew

As the chip size increases, and higher clock speed is needed for employed higher performance, the phase difference between clocks in each part of circuit becomes great enough to cause problems.

#### • High power consumption

With global synchronization parts of the circuit that are not performing any function at that time must be activated and consume power without any useful result. This also worsens the power dissipation problem in some applications.

#### • Worst case performance

Since sub-circuits which can work at higher speed must be slowed down to work with the slowest one, the cycle time of the overall circuit is that of the slowest circuit instead of the average case.

#### • Design transfer to new technology

In a design with global synchronization, a circuit design for one technology could not be used with a different technology without major adaptation.

#### • Non-modularity design

A complex circuit designed for a specific clock speed could not reuses for a different clock speed, redesign or major adaptation is required.

One solution to these problems is to give up this timing assumption. Several research groups have been successful in using asynchronous logic design to implement asynchronous circuits at different levels of design complexity. Several circuits as complex as a processor have been successfully implemented using different styles of asynchronous logic design [14, 13].

## 2.2 Asynchronous logic design

The design methodologies for asynchronous logic could be categorized by delay models, a period of time needed for digital signal transition from one logic to another in wires or circuit elements, to two models: bounded delay, and unbounded delay models. The bounded delay model assumes that delay of a circuit element or wire is bounded. The opposite is assumed in the unbounded delay model.

The circuits implemented by using these delay models can be classified to:

#### • Timed circuits

Correct operation of this circuit is dependent on the delays in circuits elements and wires.

#### • Delay-insensitive circuits

Correct operation of the circuit is independent of delays in circuit elements, and wire delays are assumed to be zero.

#### • Speed-independent circuits

Correct operation of this circuit is independent of the delays in both circuit elements and wires.

#### • Quasi-delay-insensitive circuits

This circuit is delay-insensitive with 'isochronic forks' assumption.

Isochronic forks are sets of interconnecting wires where the delay difference between the branches is zero or negligible compared to the circuit element delays.

Data passing between two circuit components in asynchronous system could be encoded in a single or a pair of wires; known as single-rail and dual-rail encoding. In the single-rail encoding one wire is needed for each bit of information or data value to represent logic '1' and '0'. In the dual-rail encoding two wires are required for every bit of information. One wire is used to represent logic '1', another is used for represent logic '0'. Signal transition in one of this pair of wires represents

Figure 2.1: Signalling protocols

the data bit value for every communication. Note that signal transition could not occur in both wires (from a pair) in the same communication, because it represents both logic '0' and '1' in the same time for one data bit which is invalid.

When using dual-rail encoding, it is possible for the receiver to determine the validity of the data sent from the sender (entire data word is sent) by detecting transitions in one of the wires of each bit wire-pair. Four possible states are possible on a wire-pair: '00' indicating that that bit is idle, '01' and '10' indicating data zero and one and '11' which is an invalid state which is never seen. By ORing together the two bits we can tell whether a data bit is being signalled or not. By ANDing (or more commonly the use of a C-element tree) each of these ORed bits across a bundle a single request signal, which indicates the validity of the data on the whole bundle, can be generated. To acknowledge a communication a single acknowledge wire is used for the whole bundle.

With single-rail encoding, explicit timing information is required for the data transfer. Data word is "bundled" with 'request' and 'acknowledge' signals with is used as timing information for the data communication. Data could be "pushed" from the sender to the receiver by sender setup data and initiates 'request' signal to the receiver, the sender must keep the data value until it receives 'acknowledge' signal from the receiver which means data has been received. Data could be "pulled" from the sender to the receiver by the receiver initiates 'request', the sender setup the data and 'acknowledge' when the data is ready to sent.

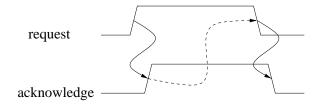

Signal transitions in the data or the request/acknowledge signal pair wires could be two-phase or four-phase. As shown in figure 2.1.

In a two-phase signalling protocol the information is transmitted by a single transition of signal as shown in figure 2.1 a. The sender initiates the communication by making a single transition on the request wire; the receiver responds by making a single transition on the acknowledge wire completing two phases of the communication. Rising and falling transitions are equivalent in the two-phase protocol.

In a four-phase signalling protocol the information is transmitted by two transitions. The sender initiates the communication by making a transition from low to high on the request wire; the receiver responds by the same transition on the acknowledge wire. The second 'return to zero' transition on both wires contains no important meaning in communication but is treated as recovery state that is used to set the signal to predefined states, as shown in figure 2.1 b.

Several asynchronous logic design styles has been developed and used so far. The favourite styles that had been applied to real circuit and implement to a very complex circuit are discussed else where [10]. One of these style that used by the AMULET group in develop its processors is Micropipelines [17].

## 2.3 Micropipelines

The Micropipeline technique, with some modifications in timing and signalling protocols, is used in the design of the AMULET processors. The Micropipelines design style, proposed by Ivan E. Sutherland, could be described as event-driven elastic pipeline (a pipeline in which the amount of data can vary). It has been used and proved to be successful as frame work of asynchronous logic design style which can be classified as bounded-delay bundled data for the data-path with delay insensitive control path [14].

Simple structure of the Micropipelines is shown in figure 2.2.

A Micropipeline uses a simple data bundle to transfer data between pipeline

Figure 2.2: Simple structure of Micropipelines

stages. Each stage could be composed of storage and processing units; communication between stages uses a request and acknowledge signal pair. Data validity is indicated by the handshake signals. Both two-phase and four-phase protocols were presented in the Micropipelines paper [17].

## 2.4 The AMULET Processors

The AMULET group research interest is in low power circuit design. Since the asynchronous logic design has potential for low power, among other things, when compared with synchronous logic, it has been used by the AMULET group to design the AMULET processors.

The AMULET3i is an asynchronous microprocessor subsystem being developed by the AMULET group at the University of Manchester. Previous research by this group also included two asynchronous processors, the AMULET1, and AMULET2e [14, 9].

AMULET1, the first asynchronous processor developed by this group, was a feasibility study of using asynchronous logic design in building a very complex circuit. The 32-bit RISC commercial processor, ARM architecture [11], was chosen mainly because it is small, simple, and a low power design; also AMULET group members had familiarity with this processor architecture and could get support for developing the processor [7].

AMULET1 was comparable in functionality to the synchronous, ARM6 processor, which was built on the same process technology. Even though the AMULET1 was no better in both performance or power-efficiency when compared with

ARM6, it met its primary goal, to show the feasibility of designing very complex asynchronous circuits [7, 14, 9].

With successful results from the design of the AMULET1, the AMULET2 group continued working on the second asynchronous processor, the AMULET2e. Because of experiences of interfacing problems between the AMULET1 processor and other chips at board level, to gain performance and to reduce power consumption, the AMULET2e was designed to be an asynchronous embedded micro-controller. It incorporated the AMULET2 processor core, on-chip memory, and an external memory interface. This memory interface can be used with ROM, RAM, or peripheral chips.

Several new features were introduced to the AMULET2 processor core, e.g. register forwarding, a branch target cache, but the most useful is the 'halt' feature which made the power consumption drop to near zero when the processor was running in an idle loop. Both performance and power-efficiency of the AMULET2e were competitive with ARM710 and ARM810, the synchronous processors. The AMULET2e was a highly usable asynchronous embedded system chip [9].

The AMULET3i is currently being developed by the AMULET group. It is designed to be suitable for commercial embedded applications. To gain performance, reduce the power consumption, and make asynchronous logic more useful in a system, the AMULET3i subsystem incorporates the AMULET3 processor core, on-chip RAM, ROM, an asynchronous bus, external memory interface, synchronous bridge, test interface and a DMA controller. The AMULET3i subsystem will be discussed in more detail in the next chapter; the DMA controller is the subject of this thesis.

## 2.5 Summary

Asynchronous logic design has been used to solve problems that exist in a very complex circuit, such as a processor subsystem. The Micropipelines, one of specific asynchronous design style has been proved to be successful method in implement two AMULET processors. The AMULET3i processor will be the latest which tries to achieve commercial viability; the DMA controller is one important component in this subsystem which will improve the system in handling data transfer more effectively.

# Chapter 3

# The AMULET3i Subsystem

## 3.1 Introduction

The AMULET3i, an asynchronous processor subsystem, is a set of macro-cells which is composed of the AMULET3 processor core and several other asynchronous components. It is designed as a part of larger chip which is intended to be used as a base unit in the low power applications.

The main components in the AMULET3i subsystem (figure 3.1) include:

- Processor-Memory Subsystem, which include:

- AMULET3 Processor Core

- Local RAM

- Processor Local Bus

- ROM

- MARBLE Bus (see section 3.2)

- DMA Controller

- Peripheral Devices

- External Memory Interface

Figure 3.1: The AMULET3i Subsystem

• Test Interface Controller

## 3.2 The MARBLE Bus

The MARBLE bus [1] is an asynchronous on-chip bus for connecting macro-cells. It supports high speed data transfer, atomic transactions and multiple initiators with central arbitration and address decoding.

Most communication between devices in the AMULET3i subsystem can be performed across the MARBLE bus. (There are some exceptions such as processor interrupt (IRQ) or peripheral request (DRQ) which are passed directly between devices). A data transfer from a one device to another device is done in one cycle via the MARBLE device interfaces.

The MARBLE bus has two types of interface: an initiator interface and a target interface. Each interface presents one address bundle and two unidirectional data bundles to its subsystem. A single data bundle from the MARBLE bus is forked to input/output data bundles on the device interfaces. The data bundle consist of a 32-bit wide data bus and a request/acknowledge signal pair. The address bundle consist of the 32-bit wide address bus and other command

Figure 3.2: The MARBLE interfaces

buses such as data size and direction (read/write) of data transfer, as shown in figure 3.2.

#### 3.2.1 Initiator Interface

The initiator interface is used by the initiator device to read or write data from or to the target device across the bus. The initiator device set up target device's address, size of data, type of the operation (read or write) on the initiator interface and sends them to MARBLE using request/acknowledge signals. The MARBLE bus receives address/command and passes it to the target device via target interface (see next section) of that device.

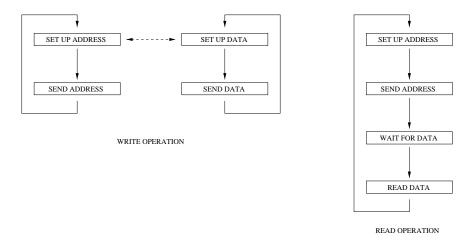

In a write operation data is sent across the bus from the initiator device to the target device. The data item is sent independently from the address. Data can be sent before, after, or simultaneously with the address to the bus. However the corresponding address and data of the same transfer must be sent before next transfer may be started, data and address of different transfer cannot not overlapped in sending/receiving.

Figure 3.3: Initiator interface data transfer operations

In a read operation, a data item is transferred from the target device to the initiator device across the bus. The target device is finishes receiving the address before it can determine the address and command and send the data back to the initiator device.

A diagram of data read/write operations performed by the initiator device is shown in figure 3.3.

## 3.2.2 Target Interface

The target interface is used by the target device to receive addresses and read or write data to or from the initiator device across the bus. The target device determines the operation (read or write) from address/command sent by the initiator device before performing the corresponding operation.

In a write operation the target device waits for data from the initiator; in a read operation a data item is returned from the target device to the initiator device.

A diagram of data read/write operations performed by a target device is shown in figure 3.4.

Figure 3.4: Target interface data transfer operations

## 3.2.3 Type of data transfer

The bus supports data transfers between an initiator and a target device. In DMA, transfers between two target devices must be achieved. There are two general methods of approaching this:

#### • Store-and-Forward

Data transfer between two different target devices is controlled by an initiator device. The transfer is done in two cycles: a read-cycle and a write-cycle consequently. In the read-cycle, the initiator reads data from the source device; in the write-cycle, the data is written from the initiator to the destination device.

#### • Fly-past

Data transfer between two different target devices is transferred in one cycle. In this type of transfer the read request to the source device and the write request to the destination device are initiated simultaneously. The data item is transferred directly from the source device to the destination device in one cycle.

Fly-past transfer is more efficient than store-and-forward transfer, however it cannot be used for transferring data between two different regions in the same device; e.g. memory to memory transfer on the same memory device could not done by this method. The current implementation of the MARBLE bus supports only store-and-forward data transfers.

## 3.3 Processor-Memory Subsystem

Unlike the other components of AMULET3i which are linked by the MARBLE bus, the processor and local RAM form a close-coupled group with local buses. Separating the processor core and local RAM from other parts of the system allows the processor to access local RAM more effectively, since it avoids the impediment of the full, multi-master bus control. These local buses also reduce traffic on MARBLE since instructions and data which the processor use frequently can be stored in local RAM, leaving MARBLE free to be used by other devices.

There is some penalty when the processor needs to access other parts of memory outside the local RAM or other devices on MARBLE, however some of this penalty can be overcome by using the DMA controller to transfer data from that part of memory to local RAM.

The processor-memory subsystem connects to MARBLE as a single component with two initiator interfaces (one for the instruction bus and another one for the data bus) and one target interface. The initiator interfaces allow the processor access to instructions/data from other devices on MARBLE while the target interface allows other initiator devices access to data in the local RAM.

#### 3.3.1 The AMULET3 Processor Core

The AMULET3 processor core is implemented using ARM architecture version 4T [8]. It is functionally compatible with the ARM8 processor. Although to get the best performance the binary code could be compiled and optimized specifically

for AMULET3.

One feature of the ARM architecture which does not exist in many RISC processors are instructions to load/store multiple register values to/from memory. These instructions allow the processor to transfer several data items between device and registers with higher performance than simple load/store instructions. However, these instructions are still not applicable for transferring large amounts of data between devices, which is a functional performed more efficiently by the DMA controller.

#### 3.3.2 Local RAM

The local RAM on AMULET3i subsystem is an 8KB static memory which is divided into smaller memory blocks. The fragmenting of the local RAM into interleaved blocks means that different blocks can be accessed simultaneously on the two local buses without the expense of dual-port RAM.

In theory the local RAM could be made to work as a cache, but because of limited development time this feature is not realized in the first implementation of AMULET3 which has simply a directly memory mapped local RAM.

## 3.3.3 The Processor Local Buses

The processor local buses separate instruction and data traffic into two separate buses. The local buses allow high bandwidth memory accesses and simplify the memory-address interface. The instruction bus is connected to MARBLE via an initiator interface which is used by the processor when it fetches instructions from an external memory device. The local data bus, however, is more complex; it can be used by the processor to access data on other devices on MARBLE and by the initiator devices on MARBLE to access data on the local RAM. Therefor the local data bus is connected to MARBLE by both initiator and target interfaces. The DMA controller can access data in the local RAM via this target interface on the local data bus.

## 3.4 Other Devices

### 3.4.1 On-chip ROM

The AMULET3i ROM is an 16KB on-chip ROM connected to the MARBLE bus via a target interface. It provides application software and routines for testing the AMULET3i subsystem. Routines for testing and initializing the DMA controller could be stored on this ROM and be executed after system power up.

## 3.4.2 External Memory Interface

The external memory interface allows the AMULET3i subsystem to connect with off-chip devices, so conventional synchronous devices could be used via this interface. The interface supports direct connection of external memory and peripheral devices with 8/16 bits data width. The timing of the accesses to these off-chip devices is defined by a timing reference delay, which is only activated when an off-chip access is required. The timing characteristics and bus width are programmable separately for different memory regions. The DMA controller could be used to perform DMA transfers with these devices, however peripheral device connected via this interface could only be treated as memory device, because a peripheral request signal (DRQ) is not support by this interface.

# 3.4.3 The Asynchronous Peripheral Devices

At the time that this thesis is written, no real asynchronous peripheral devices are planned for inclusion in the AMULET3i subsystem. However, the behaviour and interface of any such devices must conform to the following specifications to work with the system and the DMA controller properly.

- Interface to MARBLE via target interface

- One or more fixed address in memory address space

- Data transfer size can be 8/16/32 bits

- Initiate data transfer by DRQ signal when it is ready to transmit or receive data

The device address is fixed and predefined, each device has a specific DRQ signal pair.

#### 3.4.4 Test Interface Controller

The test interface controller provides an external interface to a MARBLE initiator. This allows external access to all MARBLE targets for test or debug purposes. The interface is designed to suit conventional VLSI production test equipment and it therefore uses a clocked protocol.

## 3.5 The DMA Controller

The DMA controller is another device on the MARBLE bus, it is both an initiator device and target device at the same time. Design of the DMA controller will be discussed in the next chapter.

# Chapter 4

# Top Level Design

## 4.1 Introduction

The AMULET3i DMA controller is designed for a general MARBLE based system. The specifications of the DMA controller which are used as a framework of the design are mostly taken from the requirements and its environment. Those that does not in the requirements are arbitrarily chosen, some are influenced by the design of existing DMA controllers. The reasons for arbitrarily chosen specifications will be discussed in the next chapter. This chapter discusses the top level design of the DMA controller.

# 4.2 Specifications

The DMA controller specifications are:

- Four independent programmable channels

This number of channels is arbitrarily chosen, but is expandable without significant change in the structure of design. Also four DMA channels are used in the design of many existing DMA controllers, e.g. Intel 8237 DMA controller and National Semiconductor NS32230.

- 8/16/32 bit transfer sizes

As required by devices on the subsystem, these transfer sizes are supported by the MARBLE bus, and allow DMA transfers with appropriate data size for specific devices.

- Data transfer can be performed between

- Peripheral and memory

- Memory and memory

- Peripheral and peripheral

Required by the subsystem to support three types of data transfer.

- Store-and-forward transfer

- This method of data transfer is supported by the MARBLE bus, as opposed to fly-past transfer method, which is not supported. These two types of transfer were described in chapter 3.

- Interrupt enable, configurable for each channel

The IRQ signal can be used to notify the processor when data transfer for a specific channel is finished.

- Peripheral synchronization with DRQ signal

The peripheral device initiates data transfer when it is ready to transmit/receive data by using DRQ signal. Devices may be mapped onto arbitrary channels, so more than four devices can use DMA, but only four devices at a time.

# 4.3 The DMA operation overview

Arriving of the peripheral request signal (DRQ), after a channel is enabled activates the channel request mapping block in the register unit to generate the channel transfer request signal (CHANREQ) to the transfer engine. The CHANREQ activates the transfer engine to read the corresponding channel registers

from the register unit and performs data read/write with MARBLE using addresses and data transfer configurations in the channel registers. Simultaneously acknowledgement to the DRQ signal is also performed by the transfer engine after reading/writing with the peripheral device. For memory to memory transfer, no DRQ signal is needed, enable state in control registers is mapped directly by the channel request mapping block to sent CHANREQ to the transfer engine. For peripheral to peripheral DMA transfer, two DRQ signals from both source and destination devices are needed.

Detail the DMA transfer operation is discussed in next chapter.

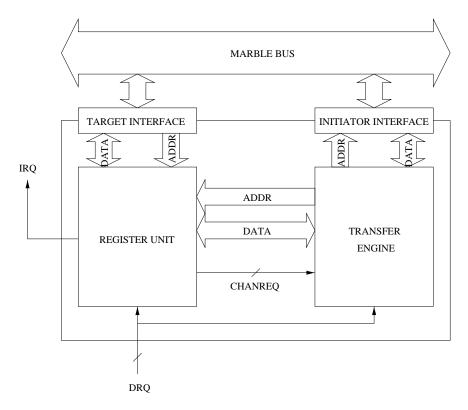

## 4.4 The DMA controller internal structure

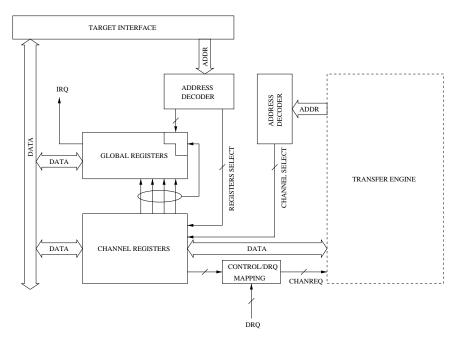

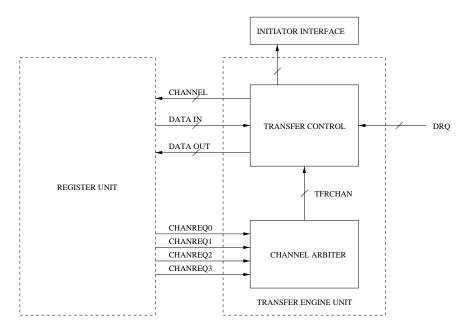

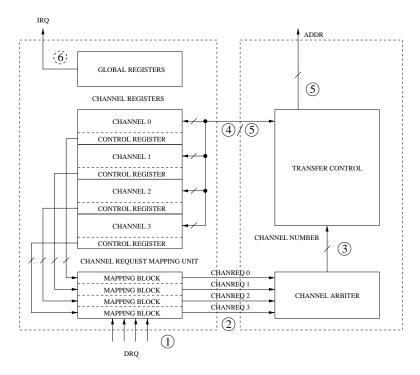

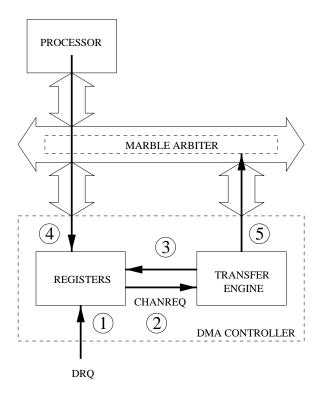

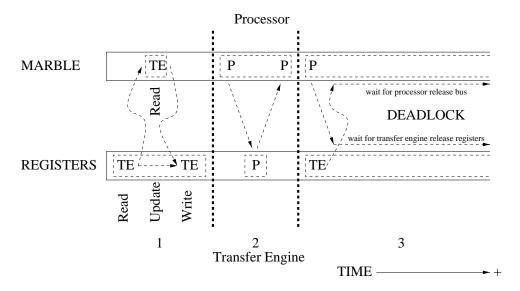

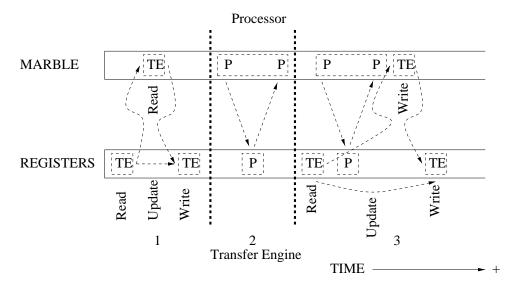

In the design of DMA controller, the internal structure can be divided into two major units: the register unit and the transfer engine unit, as shown in figure 4.1.

Each unit has its own interface to MARBLE; the register unit contains a target interface which all allows the DMA controller to be programmable by the processor via this interface, the transfer engine unit uses an initiator interface to transfer data between source and destination devices.

The transfer engine reads/writes data to/from the register unit via an internal bus. The register unit not only contains DMA registers and handles register access from the transfer engine and processor but also handles the processor request signal (IRQ) and initiates request for data transfer to the transfer engine with CHANREQ signals when a DMA channel is ready.

# 4.5 The Register Unit

The register unit contains the DMA registers and other control circuits for handling register access, IRQ, DRQ and CHANREQ signals. The registers are divided into two groups: global registers and channel registers. The global registers

Figure 4.1: Block diagram of the DMA controller

are used to control the interrupt request signal (IRQ), the channel registers are used to keep the states of the transfer operation for each channel. There are three groups of control circuits in the register unit: one used to handle access requests from the processor (via the bus interface) and the transfer engine, one to control the IRQ signal, and one to map the peripheral request signals (DRQ) and enable state (set in the control registers) to channel requests (CHANREQ) sent to the transfer engine. A diagram of the register unit is shown in figure 4.2.

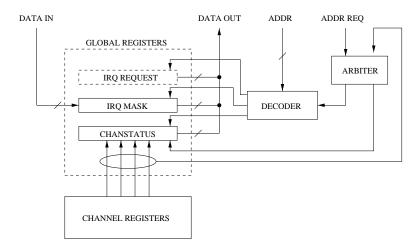

## 4.5.1 The Global Register Unit

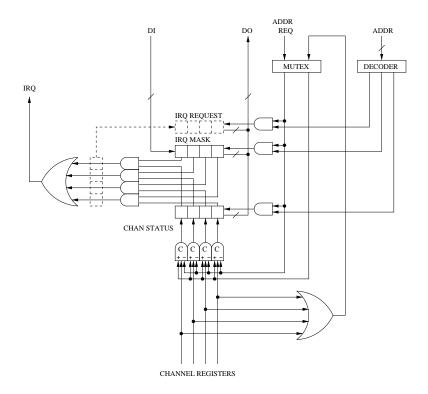

The global registers comprise:

- ChanStatus

- IRQMask

- IRQRequest

Figure 4.2: Register Unit

registers. Access from the processor to one of these registers is independent from access to channel registers. These registers are used in interrupt control and generate the interrupt request (IRQ) signal to the processor. The IRQMask register is read/writable by the processor but the other two registers are read-only. Each bit in the IRQMask register is corresponds to a DMA channel which is used to specify whether, when the data transfer for that channel has finished, the DMA controller needs to interrupt the processor or not. Each bit in the ChanStatus register also corresponds to a DMA channel which is set by the channel registers when the transfer for that channel is finished. Every bit in ChanStatus will reset when the processor performs a data read from ChanStatus or IRQRequest register. The IRQRequest register is not an actual register but is an AND operation between the ChanStatus and IRQMask register, this register provides a convenient mechanism for the processor to determine which channels caused the interrupt request.

The interrupt control circuit generates the interrupt request signal to the processor when the AND operation between IRQMask and ChanStatus registers have

Figure 4.3: Global Registers

non-zero values. The IRQ signal will change when either IRQMask or ChanStatus register value is changed, if the AND operation returns a zero value then the IRQ is removed.

A diagram of the global registers is shown in figure 4.3.

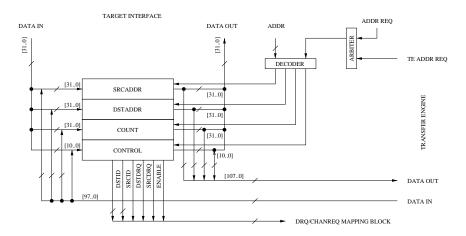

# 4.5.2 The Channel Registers

Each channel register is independent from the other channel registers and the global registers, the processor and the transfer engine can access registers on different channels simultaneously.

Each set of channel registers comprises:

- SrcAddr

- DstAddr

- Count

Figure 4.4: Channel Registers

#### • Control

registers as shown in figure 4.4.

Every register is read/writable by the processor and the transfer engine. The processor can access one register at a time, via the bus interface; this is limited by the size of the bus. The transfer engine uses a wider bus for access to channel registers, allowing the transfer engine to access all registers in a channel at once.

The SrcAddr and DstAddr are 32-bit address registers for keeping source and destination addresses respectively; this allows the DMA controller to perform data transfer across the full range of the address space. The counter is also 32 bits wide, the DMA controller can transfer up to  $2^{32}$  data items in one DMA transfer sequence.

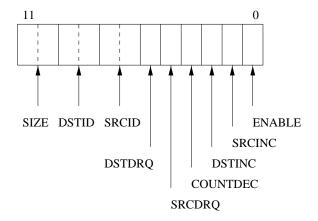

The control register is used to control the DMA transfer operation. The control functions in the the control register include:

- Enable/Disable

- Source Address increment

- Destination Address increment

- Counter decrement

- Source device uses DRQ

Figure 4.5: Control Register

Figure 4.6: Channel Request Mapping Unit

- Destination device uses DRQ

- Source device ID

- Destination device ID

- Data size

The 'device uses DRQ' and 'device ID' bits in the control register are used to map the peripheral requests signal for generate transfer request to the transfer engine.

The control bit configurations in the control register is shown in figure 4.5. The channel request mapping unit and channel mapping block are shown in figure 4.6 and 4.7.

Figure 4.7: Internal structure of Channel Request Mapping Block

## 4.6 The Transfer Engine Unit

The transfer engine unit is composed of the channel arbiter unit and the transfer control unit. The transfer engine unit, when idle, waits for requests to transfer from DMA channels in the register unit and performs data transfers for a selected channel by initiating a data transfer to the bus. Data are transferred singly. When a transfer is finished, the transfer engine becomes idle again and waits for next request.

A diagram of internal structure of the transfer engine is shown in figure 4.8.

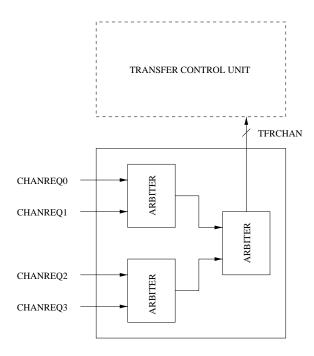

#### 4.6.1 The Channel Arbiter Unit

The channel arbiter unit arbitrates the transfer request signals sent from the channel registers in the register unit. It sends the arbitrated channel number to the transfer control unit to perform a data transfer.

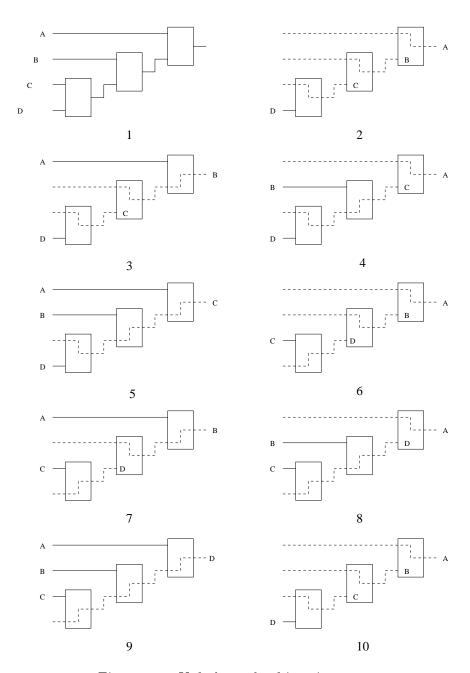

The channel arbiter uses a tree of arbiter-call elements to choose a channel from multiple channel requests. Two types of arbiter tree can be used: balanced tree, or unbalanced tree. Details of the arbiter call elements and arbiter tree will be discussed in next chapter.

A diagram of the channel arbiter is shown in figure 4.9.

Figure 4.8: Transfer Engine Unit

Figure 4.9: Channel Arbiter Unit

#### 4.6.2 The Transfer Control Unit

The transfer control unit controls the actual data transfer between the source device and the destination device. It needs to perform four separate functions:

- 1. Synchronization with the peripheral device using the DRQ signal if required (controlled by 'usedrq' and 'device ID' bits in the control register).

- 2. Read/write registers to/from the register unit.

- 3. Initiate data read/write transfer with bus.

- 4. Increment/decrement and write back registers.

When it receives an arbitrated channel number from the channel arbiter, the transfer control unit reads the selected channels registers from the register unit. Control register bits are used to determine data size, requirements for synchronization with peripheral device during data transfer, source and destination address increment, and counter decrement. The transfer control unit then performs data read/write from/to the devices by initiating address request with buses. If peripheral synchronization is required, it synchronizes with the device with DRQ signals. Simultaneously with data read/write operation, the transfer control update registers and write the updated values back to the channel register. When the operation is finished it waits for next transfer request from the channel arbiter.

## 4.7 Summary

From top level design, the DMA controller is divided into smaller parts by its functionality. The register units keep all registers and handle request for transferring data for each DMA channel and send requests to the transfer engine. It also handles interrupt request to the processor. The transfer engine performs the actual data transfer when receives a request from a DMA channel. The DMA

51

operation are performed by tightly coupled cooperation between these two major parts of the DMA controller.

The design issues and problems will be discussed in the next chapter.

# Chapter 5

# Design Issues

## 5.1 Introduction

This DMA controller is designed from its specifications (see section Specifications in previous chapter) to be a multi-channel DMA controller in which each channel supports transfers between any combination of memory and peripheral devices. There are several issues concerned in allowing the DMA controller to function correctly and efficiently as specified. This chapter discusses various important design issues, the problems, and solutions chosen to solve these problems.

# 5.2 DMA Registers

For programmability, registers are used. For each DMA channel, these values are needed:

- Source/Destination device addresses

- Number of data items to transfer

- Type of source/destination devices (memory or peripheral)

- Data size

32 bits registers are used to store these values for two main reasons:

- The processor word size is 32 bits, a read/write operation with one DMA register can be performed in one access.

- The 32 bit address register allows the DMA controller to perform data transfer with any device in the address space and for lengths of the whole address space.

## 5.2.1 Transfer Control Configurations

The control operation specifies by whether the device's address is required to increment after the transfer, and whether synchronization with a peripheral request signal (DRQ) is required. For a memory device an address increment is required and no synchronization is needed; for a peripheral device, the address is fixed and synchronization is needed, in which case a device ID must be supplied so the transfer engine can synchronize with the right device. So 'source/destination address increment' and 'device uses synchronization' are used as configurations instead of the 'type of devices'.

To allow a DMA channel to perform data transfer with a non-specific peripheral device, the device number needs to be programmable and is used when peripheral synchronization is specified. 'Source/Destination ID' is used for this configuration.

The counter is used to control the number of data items to transfer, but also to allow a 'free run' type of transfer, in which the DMA controller performs data transfers continuously until it is stopped by the processor. A 'counter decrement/free run' configuration is used to tell the DMA controller to decrement the counter after each data transfer or just to ignore the value of the counter. The 'enable/disable' mechanism to start and stop the DMA transfer is required for the 'free run' type of transfer.

To save registers and allow the processor to program a DMA channel more

conveniently all transfer control configurations are stored as bits field in one register, called the control register. The bit field configuration in the control register is shown in figure 4.5.

## 5.2.2 Processor Interrupt Control Configuration

After the data transfer for a channel is finished, a mechanism to notify the processor is necessary. An interrupt mechanism is chosen for this purpose. However an interrupt costs the processor with a context switch to an interrupt service routine, so a mechanism to allow the processor to specify which channels should send an interrupt when the transfer is finished is also necessary to eliminate unwanted interrupts. The 'interrupt enable' configuration is used. This could be a bit field stored in the control register like other control configuration; however if the processor needs to disable all interrupts from the DMA controller, it has to write to every control register which is not convenient. Instead, the 'interrupt enable' bits for all DMA channels are stored together in one register called 'IRQ Mask' which allows the processor to disable/enable every channel with one register access.

# 5.3 DMA Operation

The DMA controller, after being programmed and enabled by the processor, can start performing data transfers when the source/destination devices are ready to transmit/receive data.

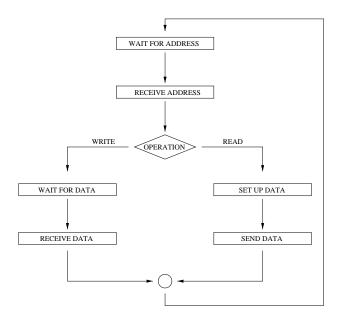

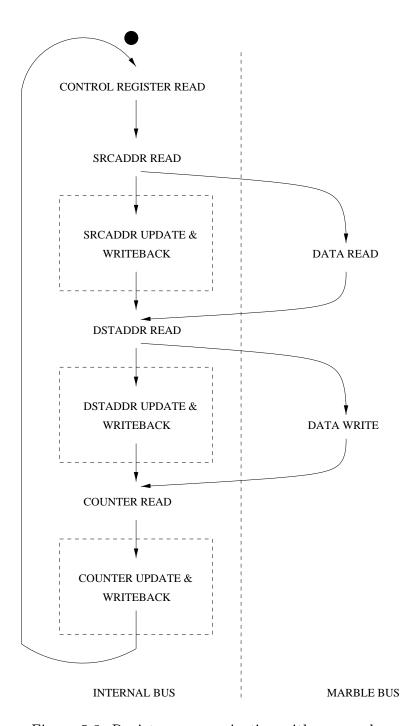

## 5.3.1 DMA Operation Overview

The DMA operation starts at the channel request mapping block in the register unit (figure 5.1). This sends a channel transfer request signal (CHANREQ) to the channel arbiter unit in the transfer engine when both source and destination devices are ready to transfer data. The channel arbiter then arbitrates and selects a channel; it sends the channel number to the transfer control unit. The transfer

Figure 5.1: Sequence of the DMA operation

control unit uses the channel number to read the appropriate channel registers and performs a data transfer for that channel. It updates all corresponding registers with respect to the configurations in the control register and performs necessary functions to stop the data transfer operation and notify the processor if the last data item for that channel has been transferred.

The DMA operation can be divided into three sub-operations:

- Channel selection operation

- Data transfer operation

- Stop transfer operation

## 5.3.2 Channel Selection

Each channel request mapping block works independently if a DMA channel is enabled, and source and destination devices for that channel are ready, a CHAN-REQ signal will be sent from the register unit to the channel arbiter unit in the

transfer engine. If several requests occur, one must be selected from these. Arbitration is used to grant exclusive access to the single transfer engine to just one request at a time.

In the existing synchronous DMA controllers, both prioritized and non-prioritized schemes can be applied to select a requesting channel. However the nature of asynchronous circuit is different; no global clock is used to judge the simultaneous arrival of events. Unlike a synchronous system where the stability of signals is assured before an active clock edge an asynchronous system cannot 'sample' incoming requests as there is no safe time period during which all the inputs remain stable.

Instead an arbitration tree (discussed later in section Arbitration) can be used to select a channel; this gives a fairly small circuit and allows the transfer engine to start the data transfer as soon as possible.

## 5.3.3 Data Transfer Operation

The transfer between devices is performed on the bus, the DMA controller acting as an initiator device. A read followed by a write cycle is performed.

The transfer control unit starts the data transfer operation when a channel is selected by the channel arbiter unit. The operation starts by the transfer control reading the channel registers from the register unit. These register values are used to control the data transfer operation.

The data transfer operation can be divided into two subsequence operations: 'read operation' and 'write operation'.

In the 'read operation', the transfer control initiates a 'data read' transfer from the source device. The source device address is taken from the SrcAddr register and data size is taken from the control register; these values are required to initiate the transfer. If the source device needs peripheral synchronization, the transfer control also acknowledges the device when data is received.

After getting the data from the source device, the transfer control unit performs the 'write operation' sending the data to the destination device in the same manner as it performs the 'read operation', but destination address and other destination device's configurations are used instead of the source device configurations; so 'data write' transfer is performed with the destination device.

During the 'read/write operations' which the transfer control performs with the bus, register update and write back operation can be performed concurrently with the register unit. 'Source/destination addresses increment' and 'Counter decrement' configurations in the control register are used to determine the necessity of specific register updating. The additional operation 'channel disable' in which the enable bit in the control register is reset to stop data transfer for that channel is also performed if the counter value is decremented to zero.

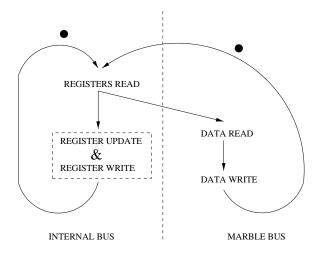

### 5.3.4 Register Communication Models

Communication between the transfer control unit in the transfer engine and the channels register in the register unit could use two different models with respect to size of data bus connecting them. This is different from communications between the DMA controller and MARBLE which is restricted by the MARBLE interfaces; only a narrow bus can be used.

#### Wide Bus Communication

This model uses a wide bus for communication, all registers in a channel are read/written at once. This allows register value transfer between these two internal units in the DMA controller with high efficiency, although it also costs a number of wires and the transfer control needs extra storage to store the register value needed in the later sequence of the 'data write' operation.

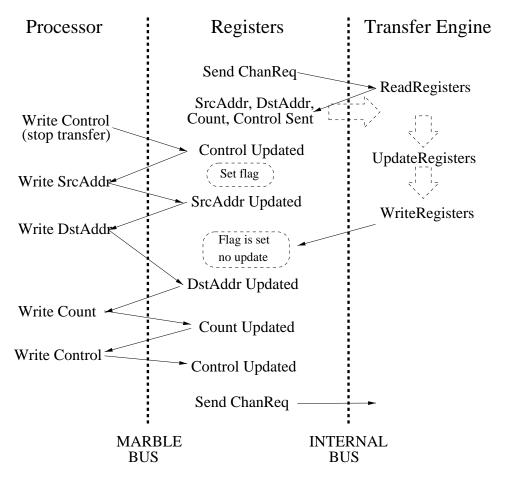

A diagram of the register communication using wide internal bus is shown in figure 5.2.

Figure 5.2: Register communication with wide bus

#### Narrow Bus Communication

This model uses a narrow bus for communication, only one register can be read/written at a time. The transfer control unit would start the communications by reading control register to determine the transfer configurations first. Initiating a data read from the source device requires 'data size', 'source device uses synchronization', and 'source device ID' configurations from the control register. The values of the control register are stored for later used.

The transfer control then reads the SrcAddr register and performs a 'data read' operation (with MARBLE), if a source address increment after the data transfer is required the source address will be added to the 'data size' and the new value is written back to the register unit. The 'data read' operation and 'source address update/write-back' operation can be performed concurrently.

After the data is received from the source device, the 'data write' operation is performed after the transfer control unit has read the DstAddr register from the register unit. Data is written to the destination device concurrently with DstAddr updating and write-back in the same manner with the read operation.

If the 'counter decrement' configuration is set, the transfer control updates the counter register by reading the Count register, decrementing it and writing the new counter value back to the register unit. If the new counter value is zero, the channel disable is also performed when the counter register is written back.

A diagram of data transfer operation using narrow internal bus width is shown in figure 5.3.

By comparing figures 5.2 and 5.3 it can be seen that the control operation when using a wide bus is much simpler than when using a narrow bus. In this design the wide bus is chosen.

The independence of the MARBLE bus read/write operations and register read/write operations could lead to a problem when the last data item is transferred. If a channel is set to interrupt the processor (depending on the corresponding bit of IRQ Mask register) the processor could be interrupted before the data transfer is finished, since the operation performed within the DMA controller (writing new register value to the register unit) will be faster than the data transfer performed with the bus (read from source device to DMA controller and write from DMA controller to destination device). To solve this problem the register updating/writing operation for the last transfer must take place after the transfer operation is completed.

## 5.3.5 Stop Transfer Operation

The stop transfer operation is performed after the last data item of a DMA sequence is transferred. Since the enable configuration in the DMA channel control register is used for sending the request for data transfer to the transfer engine, this configuration must be changed before the DMA operation is completed, otherwise the transfer engine may receive the next request for transfer even though all data items have been transferred.

The stop transfer operation is performed when the values of counter equals zero after updating. The transfer control unit writes a disable channel value to the control register. Since the only configuration bit that needs to be changed is the enable bit, writing to the control register will automatically set the enable bit to its 'disable' value.

Figure 5.3: Register communication with narrow bus

After the enable state in a channel's control register is changed to 'disable', the corresponding bit in the 'ChanStatus' register is set by a request from the channel's control register. The global register unit which contains 'ChanStatus' and 'IRQMask' registers and handles the interrupt request signal performs an AND operation between these two register values and raises the IRQ signal if the result of AND operation is not zero. A diagram of the global registers and how they relate to the IRQ signal is shown in figure 4.3.

This mechanism simplifies the operation of handling the IRQ signal, when the processor reads from ChanStatus or IRQRequest registers; the ChanStatus register value will be reset and the IRQ signal will be dropped. The processor writing to the control register when programming a DMA channel will cause the corresponding bit in the ChanStatus register to reset.

## 5.4 Shared resources in the DMA controller